NANDフラッシュの後を継ぐ技術は?

プレーナNAND以外にもフラッシュメモリーの後継技術が続々と登場してきた。

Storage Magazine10月号より

Jim Handy

フラッシュメモリーは、Intelが1988年に最初のNORチップを出荷するやいなやたちまち頭角を現した。そのNORは、3年後に登場するNANDフラッシュに道を作った。NANDはわずか10年で売上が18億ドルから180億ドルに跳ね上がるという、半導体史上最速の普及を達成した。2017年には、NAND技術の売上は500億ドルを記録した。これは1990年の半導体の世界市場規模に相当する。NANDフラッシュは明らかに巨大なビジネスだ。しかし、業界が後継候補としていくつかのメモリー技術を開発するようになって、状況は変わりつつある。

NANDフラッシュが直面する限界

過去40年間、ムーアの法則のおかげで1年~2年おきに1ビットのサイズを平均30%削減することにより、半導体チップ上のトランジスター数は倍々に増えてきた。これは結果的にコスト削減につながり、チップの用途を広げることになった。この30%の削減はプロセスシュリンクと呼ばれる。また、現在も進行中の絶え間ないサイズとコストの削減現象は、スケーリングとして知られている。ほとんどの半導体メーカーにとって、このシュリンクは将来にわたって続いていくはずだった。しかし、フラッシュメモリーには、一つの問題があった。フラッシュ内では、ビットはフローティングゲート上の電子として保存される。フローティングゲート上で保持できる電子の数は、トランジスターのサイズに比例する。15ナノメーター(nm)のプロセスジオメトリーで、わずか数十個の電子の状態が1なのか0なのか、デジタルチップのノイズの中からその差異を検出するのは極めて難しい。もしメーカーが、これまでやってきたようにトランジスターのサイズをもう30%削減したら、電子の数は検出可能なレベルに達しなくなるだろう。半導体市場全体が、現行のコスト削減を前提として成り立っている。フラッシュの価格低下に急ブレーキがかかるようでは、これは成り立たなくなる。プレーナNANDのスケーリングが壁に突き当たっている中で、コスト削減を続けるためにはどうしたらよいのだろうか?

救世主3D NAND

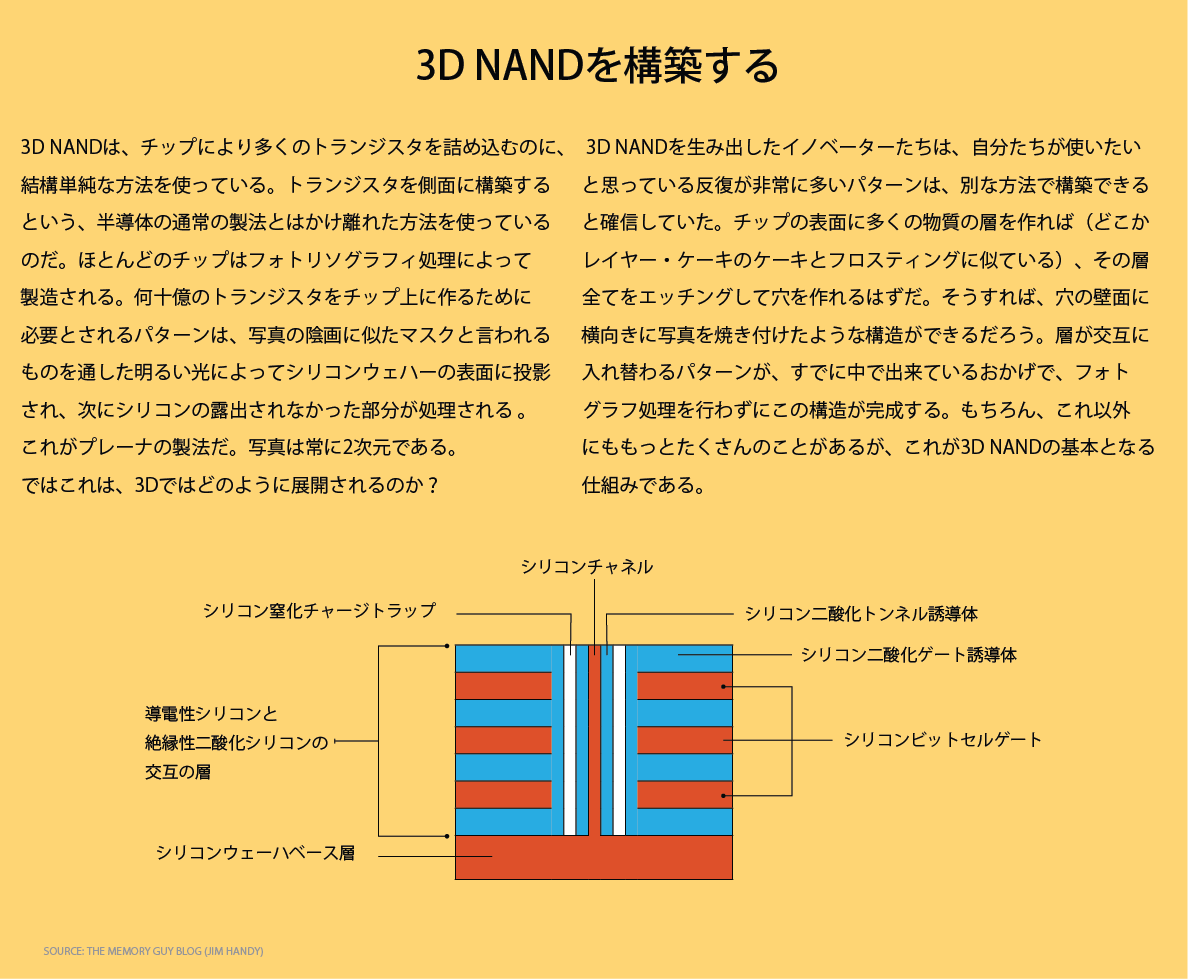

東芝は2006年に巧みなソリューションを世に出した。チップ上に構築したトランジスターをシュリンクし続けるのではなく、垂直な構造を作成し、そのタワーの壁に沿ってトランジスターを都市のオフィスビルの壁上に作られた垂直庭園のように構築してはどうか?地上に庭を造るだけの十分なスペースがないのなら、自分のビルの壁の上に作れ、ということだ。東芝は、チップ上のトランジスター数を増やすこの手法を用いて、たとえトランジスターがスケールできなくても、フラッシュ・ビットのコスト・スケーリングを継続する計画を立てた。この手法はBit Cost Scaling、略してBiCSと名付けられ、3D NANDフラッシュの土台となった。BiCSが可能にしたのは、コスト削減の継続だけではなかった。3D NANDとプレーナNANDは再設計がほとんどいらないほど似ているので、相互に使いまわしができるため、BiCSはNANDフラッシュの継続的使用もサポートしている。消費者が2個のUSBフラッシュドライブを持っていて、片方は3D NAND、もう片方はプレーナNANDだとしても、消費者にはその違いは分からないだろう。これは他の新しいメモリー技術に対して優位な点だ。

業界は東芝の手法を採用した。BiCSでは幾層にも連なった半導体の層に作られた穴を埋める柱の中にビットが構築される。その結果、次の質問はこうなった。我々はどれ位の高さまでこの垂直のタワーを建てられるのか?ここがわからない。東芝が初めてBiCSを開発したとき、柱の中のビットはチップ内の層の数と柱を作るのにつかわれる穴の広さと深さに制限されるだろう(「3D NANDの構築」参照)と言うのが一般的に信じられていた考え方だった。メーカーは、この穴を約20nmより小さくは作れない。というのは、内部にいくつか同心円状の物質の層を塗らなければならず、この同心円状の層の厚さに対する最小値は決まっているからだ。一方、深さは垂直の層の数に比例し、層にも厚さの最小値がある。これらの制限のために、穴のアスペクト比(深さを直径で割ったもの)は、フラッシュの垂直の層によって決められる。40対1のアスペクト比は製造するのが難しい。まして60対1ともなれば至難の技だ。しかし、層の数が増えるにつれて、より高いアスペクト比が求められる。そのため、3D NANDが新技術に人気を奪われて捨てられるまでの寿命は、せいぜい3世代あるいは100層が限界だろうと思われた。

だが、半導体の研究者たちは驚くほど想像力に富む集団である。彼らは、相当な数の層に対応するために、ストリング・スタッキングという新しい考え方をひねり出した。ストリング・スタッキングによって、一定の層数の3D NANDが作られ、その上にもう一つの層のセットが構築される。新しい層のセットごとに穴が作られる。しかし、この穴は少ない数の層にエッチングされるため、アスペクト比は小さいままだ。例えば、Micron Technologyは、非常に難しい64層に穴をエッチングする代わりに、32層に2回穴をエッチングして現在の64層3D NANDを生産している。これは、2つの30対1のアスペクト比の穴と1つの60対1のアスペクト比の穴の違い、とも言えるだろう。ストリングが限界に達するまで、何回スタックできるか、誰も知らない。一般的に考えられている限界は500層だが、はっきりしたことはわからない。半導体の世界では通常の考え方が間違いだと証明されることがよくある。今日(こんにち)の64層チップの密度は1テラビット(128GB)まできており、500層のチップならその10倍近いデータが保存できると考えられる。1テラバイトのチップは当然あり得る。もし、1テラバイトチップを500層のプロセスで作るとしても、今日(こんにち)の大容量チップ64層128GBより大きくはならないだろう。

ストリング・スタッキングがもたらした究極の影響とは、3D NANDがこれからも長い間生き延びるということだろう。

3D XPointはどうなのか?

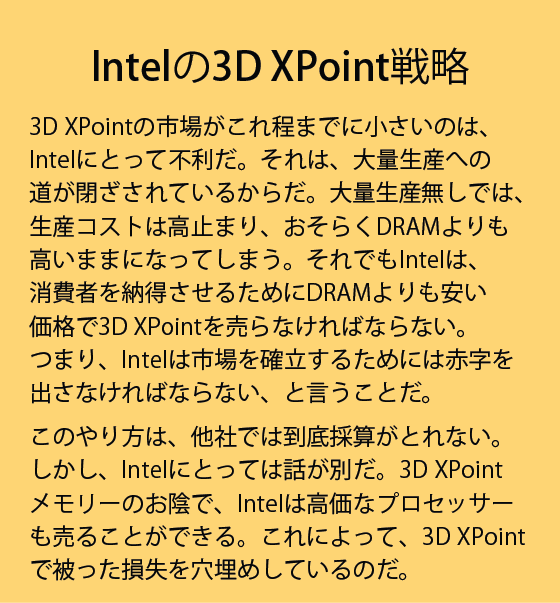

2015年、IntelとMicronは3D XPointと呼ばれる新しいタイプのメモリーを発表した。この今までのものとは異なる技術は、DRAMとNANDフラッシュの中間の価格でDRAM並みのスピードを宣言した。目指すのは、コンピューターのコスト・パフォーマンスを改善するためにメインメモリのDRAMとNAND SSDの間に新しいメモリーの階層を挟み込むことである。3D XPointは、NANDフラッシュやDRAMの置き換えとして意図されていないにもかかわらず、実際は一定のパフォーマンスを達成するためにシステム内で必要とされるDRAMの容量を減らすために使われる事が多いようだ。フラッシュやDRAMがスケーリングの限界に達すると、それに入れ替わる新しいメモリーの技術が待っているというこれまでの歴史からすれば、これは大きな変化だ。今日現在、3D XPointはPCIe Nonvolatile Memory Express(NVMe)のインターフェースにしか使われていない。NVMeはSSDのインターフェースとしては最速だが、3D XPointメモリーが本来持っている速度に比べれば遅い。実際、IntelとMicronがXPointはNANDフラッシュの1000倍速いと公言しているにもかかわらず、現在のIntel Optane SSDの速度はライバルのNANDフラッシュ製品のわずか6倍~8倍だ。3D XPointのDRAM並みの速度を引き出し、そのコスト・パフォーマンスを利用するには、明らかにDIMMインターフェースが必要だ。IntelはDIMMフォーマットの3D XPointを出荷すると明言しているが、そのような製品はまだ公式には市場に出てきていない。とはいえ、2018年のフラッシュ・メモリーサミットで、IntelはこのDIMM製品をGoogleに出荷したことを明らかにした。Objective Analysis社の2015年3D XPointメモリーに関するレポートは、3D XPointにとって最も重要な市場はサーバーのDIMMになるだろうと予測している。我々は今もこの予測を支持する。現在の3D XPointメモリー市場は比較的小さく、その内訳はほんのわずかなパフォーマンス改善に多額の出費をいとわないゲーマーで成り立っている(「Intelの3D XPoint戦略」参照)

その他の新興メモリー技術

3D XPointは調査対象となった新しいメモリー技術のほんの一例に過ぎない。中には相変化メモリ(PCM)のように相当長い期間開発されてきたものもある。この技術については50年ほど前の1970年にIntelのゴードン・ムーアが共著で記事を書いている。

これらの技術は、高パフォーマンス、低電力、不揮発性、そして最も重要なものとして、DRAMやNANDフラッシュのスケーリング限界を超える能力を謳っている。しかし、NANDフラッシュやDRAMの開発者は、次々とスケーリング限界を迂回する方法を見つけており(3D NANDはその素晴らしい例だ)、新しい技術がNANDとDRAMに置き換わるタイミングを先延ばししている。ひとつまたは複数の新技術が花開く可能性が最も高いのは、組み込みメモリーの市場だ。しかし、これらの技術のひとつがDRAMまたはNANDフラッシュと置き換わるチャンスをつかむには、相当時間がかかるかもしれない。組み込みメモリーは新しい技術をいち早く採用するだろう。論理チップ上のメモリーを、ASIC、マイクロコントローラー、マイクロプロセッサーを製造するために使われる論理プロセス上に構築するには、それが簡易で経済的でなければならないからだ。

このようなチップの中で最も一般的なNORフラッシュは、14nmという小さなプロセスを使ったラボ・プロトタイプが構築されているものの、45nm以上のスケーリングで手こずっている。同様にスタティックRAMでさえも、SRAMビットのサイズをプロセスに比例してスケーリングするのに失敗していて、問題を抱えていることが明らかになっている。これによってSRAMチップの比例的増大が危機にさらされ、ASIC、マイクロコントローラー、マイクロプロセッサーがより小さなプロセスにスケーリングすることで実現するメリットが制限されてしまう。NORやSRAMに取って替わろうと、新しいメモリー技術が待ち構えている。ここに上げるのはその数例だ。

■磁気抵抗メモリー(Magnetoresistive RAM:MRAM)

HDDヘッドの製造ですでに大量生産に入っている磁気技術がベース。Everspin Technologiesは、スタンドアローンのメモリーとしてこの不揮発性の技術を約5年間作ってきており、組み込み型のバージョンは主要な工場全てで開発されている。MRAMはDRAMのような1トランジスターのセルがベースになっているため、DRAMに対しては価格優位性を保てるが、NANDフラッシュには劣る。

■相変化メモリー

IntelとMicronの3D XPointメモリーのベースになっている技術。10年程前、NORフラッシュの代替として生産に入ったが、この技術を導入したのは、Intel、Samsung、STMicroelectoronicsだけで、いずれの会社も製造を中止している。

■強誘電体メモリー(Ferroelectric RAM:FRAM)

20年以上前から生産されているが、鉛の化合物が下層のシリコンのインテグリティを劣化させる信頼性の問題のために普及には限界があった。この問題にもかかわらず、富士通は、おそらく他のメモリーを合わせた以上のFRAMベースのチップを生産してきた。新たな研究により、酸化ハフニウムという、より親しみ易く分かり易い物質が強誘電層として機能することを突き止めて、新たな関心を呼んでいる。

■導電性ブリッジメモリー(Conductive-Bridging RAM:CBRAM)

カルコゲナイドガラスを通過する金属フィラメントのマイグレーションをベースとしている。このタイプのメモリーを出荷している会社はAdesto Technologyのみである。

■抵抗変化型メモリー(Resistive RAM: ReRAM)

この技術を開発しているCrossbar社は前述のCBRAMと何かしら似たサンプルを抽出している。ナノメタルのフィラメントが、カルコゲナイドガラス層を通して成長する、というものだ。抵抗変化型メモリーは、内部セレクター機構を含むある種のビットセルを開発し、ビットセルで移動する別のセレクターを開発する必要をなくすとともに、生産プロセスを単純化した。

■Oxygen depletion RAM(OxRAM)

酸素イオンがカルコグナイドガラスから除かれて導電性の通路を形成する、というCBRAMと同様の現象をベースにしている。この技術は生産には入っていない。一年前までは、Hewlett Packard Enterpriseが、The Machineという名の自社の先進的コンピューターにOxRAMを使う計画を立てていた。しかし、Memristorと呼ばれるこのアプローチは、最近まで計画が延期されていた。

■ナノチューブRAM(Nanotube RAM:NRAM)

Nantera社が提供するこの技術は、電気的に圧縮や拡大が可能で高抵抗または低抵抗状態を作り出すカーボンのナノチューブをベースにしている。

MRAM以外は、これらの技術は全て2ターミナルセレクターをベースにしている。これらのセレクターは4f2、つまりチップに光学的にプリントした最小サイズの4倍という小さなビットセルのサイズに対応している。これらの技術は3D XPointメモリーと同様、コストの低下が期待される技術としてひとまとめにできる。

酸化ハフニウムの使用可能性が最近になって発見されるまでは、上記の技術は全て下層のシリコンほどには知られていない新しい物質を使うことが必要だった。これらの技術の採用は、このリスクのために停滞していた。新しい物質が大量生産の障害になる可能性があるからだ。

これらの技術が現在普及しているメモリーに置き換わるのを阻んでいる最も大きな要因はコストである。全てがDRAMやNANDフラッシュより何倍も高価で、特殊な機能がその法外な値段を相殺するようなニッチなアプリケーション以外は使用を見送られている。FRAMの場合、その機能とは低電力・高速書き込みだ。NRAMの場合、それは高速書き込みと信頼性のないバッテリー不要の不揮発性だ。

PCMは放射線への高い耐性から衛星に使われているし、CBRAMも同様の理由から、殺菌・消毒のために大量のX線が使われる外科の医療器具に使われている。とはいえ、これらの技術が充分に大量生産されるまでは、現在普及しているメモリーに置き換え可能なレベルの低価格をどれも実現できそうにない。市場がない限り、大量生産は起こらない。そして価格が下がらない限り、市場は開発されない。これはニワトリ・タマゴ問題である。

これからの10年間に起きること

NANDフラッシュは、少なくともあと10年は現役でいると思われる。DRAMも同様だ。Intelが3D XPointの目標を達成すれば、大量生産のフェーズに入る筈だ。しかし、おそらくそこまで行く前に、損切りのためにこの技術を売らざるを得なくなるだろう。その他の新メモリー技術は比較的近い時期にオンチップ・メモリーの後継となるだろう。しかし、DRAMおよびNANDフラッシュチップと互角に戦う日は当分来そうにない。

Jim Handyは、Objective Analysis社(カリフォルニア州ロサンゼルス)の半導体とSSDのアナリスト。

Copyright 2000 - 2019, TechTarget. All Rights Reserved, *この翻訳記事の翻訳著作権は JDSF が所有しています。

このページに掲載されている記事・写真・図表などの無断転載を禁じます。

恋塚正隆の連載コラム

恋塚正隆の連載コラム 恋塚正隆の連載コラム

恋塚正隆の連載コラム 恋塚正隆の連載コラム

恋塚正隆の連載コラム JEITA連載寄稿

JEITA連載寄稿 「Storage Magazine」

「Storage Magazine」